## 6. Recommended HDL Coding Styles

QII51007-8.0.0

#### Introduction

HDL coding styles can have a significant effect on the quality of results that you achieve for programmable logic designs. Synthesis tools optimize HDL code for both logic utilization and performance. However, sometimes the best optimizations require human understanding of the design, and synthesis tools have no information about the purpose or intent of the design. You are often in the best position to improve your quality of results.

This chapter addresses HDL coding style recommendations to ensure optimal synthesis results when targeting Altera® devices, including the following sections:

- "Quartus II Language Templates" on page 6–2

- "Using Altera Megafunctions" on page 6–3

- "Instantiating Altera Megafunctions in HDL Code" on page 6–4

- "Inferring Multiplier and DSP Functions from HDL Code" on page 6–7

- "Inferring Memory Functions from HDL Code" on page 6–13

- "Coding Guidelines for Registers and Latches" on page 6–40

- "General Coding Guidelines" on page 6–52

- "Designing with Low-Level Primitives" on page 6–81

For additional guidelines on structuring your design, refer to the *Design Recommendations for Altera Devices and the Quartus II Design Assistant* chapter in volume 1 of the *Quartus II Handbook*. For additional hand-crafted techniques you can use to optimize design blocks for the adaptive logic modules (ALMs) in many Altera devices, including a collection of circuit building blocks and related discussions, refer to the *Advanced Synthesis Cookbook: A Design Guide for Stratix II and Stratix III Devices*.

For style recommendations, options, or HDL attributes specific to your synthesis tool (including Quartus® II Integrated Synthesis and other EDA tools), refer to the tool vendor's documentation or the appropriate chapter in the *Synthesis* section in volume 1 of the *Quartus II Handbook*.

#### Quartus II Language Templates

The Quartus II software provides Verilog HDL, VHDL, AHDL, Tcl script, and megafunction language templates that can help you with your design.

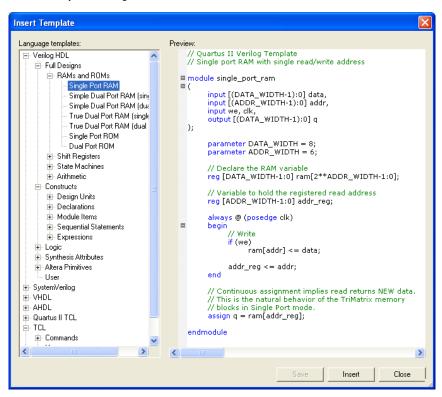

Many of the Verilog HDL and VHDL examples in this document correspond with examples in the templates. You can easily insert examples from this document into your HDL source code using the **Insert Template** dialog box in the Quartus II user interface, shown in Figure 6–1.

To open the Insert Template dialog box when you have a file open in the Quartus II Text Editor, on the Edit menu, click **Insert Template**. Alternatively, you can right-click in the Text Editor window and choose **Insert Template**.

Figure 6-1. Insert Template Dialog Box

#### Using Altera Megafunctions

Altera provides parameterizable megafunctions that are optimized for Altera device architectures. Using megafunctions instead of coding your own logic saves valuable design time. Additionally, the Altera-provided megafunctions may offer more efficient logic synthesis and device implementation. You can scale the megafunction's size and set various options by setting parameters. Megafunctions include the library of parameterized modules (LPM) and Altera device-specific megafunctions.

To use megafunctions in your HDL code, you can instantiate them as described in "Instantiating Altera Megafunctions in HDL Code" on page 6–4.

Sometimes it is preferable to make your code independent of device family or vendor. In this case, you might not want to instantiate megafunctions directly. For some types of logic functions, such as memories and DSP functions, you can infer a megafunction instead of instantiating it. Synthesis tools, including Quartus II integrated synthesis, recognize certain types of HDL code and automatically infer the appropriate megafunction. The synthesis tool uses the Altera megafunction code when compiling your design—even when you do not specifically instantiate the megafunction. Synthesis tools infer megafunctions to take advantage of logic that is optimized for Altera devices or to target dedicated architectural blocks.

In cases where you prefer to use generic HDL code instead of instantiating a megafunction, follow the guidelines and coding examples in "Inferring Multiplier and DSP Functions from HDL Code" on page 6–7 and "Inferring Memory Functions from HDL Code" on page 6–13 to ensure your HDL code infers the appropriate Altera megafunction.

You must use megafunctions to access some Altera device-specific architecture features. You can infer or instantiate megafunctions to target some features such as memory and DSP blocks. You must instantiate megafunctions to target certain device and high-speed features such as LVDS drivers, PLLs, transceivers, and double-data rate input/output (DDIO) circuitry.

For some designs, generic HDL code can provide better results than instantiating a megafunction. Refer to the following general guidelines and examples that describe when to use standard HDL code and when to use megafunctions:

- For simple addition or subtraction functions, use the + or symbol instead of an LPM function. Instantiating an LPM function for simple arithmetic operations can result in a less efficient result because the function is hard coded and the synthesis algorithms cannot take advantage of basic logic optimizations.

- For simple multiplexers and decoders, use array notation (such as out = data[sel]) instead of an LPM function. Array notation works very well and has simple syntax. You can use the lpm\_mux function to take advantage of architectural features such as cascade chains in APEX™ series devices, but use the LPM function only if you understand the device architecture in detail and want to force a specific implementation.

- Avoid division operations where possible. Division is an inherently slow operation. Many designers use multiplication creatively to produce division results.

#### Instantiating Altera Megafunctions in HDL Code

The following sections describe how to use megafunctions by instantiating them in your HDL code with the following methods:

- "Instantiating Megafunctions Using the MegaWizard Plug-In Manager"—You can use the MegaWizard® Plug-In Manager to parameterize the function and create a wrapper file.

- "Creating a Netlist File for Other Synthesis Tools"—You can optionally create a netlist file instead of a wrapper file.

- "Instantiating Megafunctions Using the Port and Parameter Definition"—You can instantiate the function directly in your HDL code.

## Instantiating Megafunctions Using the MegaWizard Plug-In Manager

Use the MegaWizard Plug-In Manager as described in this section to create megafunctions in the Quartus II GUI that you can instantiate in your HDL code. The MegaWizard Plug-In Manager provides a graphical user interface to customize and parameterize megafunctions, and ensures that you set all megafunction parameters properly. When you finish setting parameters, you can specify which files you want to be generated. Depending on which language you choose, the MegaWizard Plug-In

Manager instantiates the megafunction with the correct parameters and generates a megafunction variation file (wrapper file) in Verilog HDL (.v), VHDL (.vhd), or AHDL (.tdf) along with other supporting files.

The MegaWizard Plug-In Manager provides options to create the following files:

- A sample instantiation template for the language of the variation file (\_inst.v | vhd | tdf).

- Component Declaration File (.cmp) that can be used in VHDL Design Files

- ADHL Include File (.inc) that can be used in Text Design Files (.tdf)

- Quartus II Block Symbol File (.bsf) for schematic designs

- Verilog HDL module declaration file that can be used when instantiating the megafunction as a black box in a third-party synthesis tool (\_bb.v).

- If you enable the option to generate a synthesis area and timing estimation netlist, the MegaWizard Plug-In Manager generates an additional synthesis netlist file (\_syn.v). Refer to "Creating a Netlist File for Other Synthesis Tools" on page 6–6 for details.

Refer to Table 6–1 for a list and description of files generated by the MegaWizard Plug-In Manager.

| Table 6–1. MegaWizard Plug-In Manager Generated Files (Part 1 of 2) |                                                                                                                      |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| File                                                                | Description                                                                                                          |

| <output file="">.v (1)</output>                                     | Verilog HDL Variation Wrapper File—Megafunction wrapper file for instantiation in a Verilog HDL design.              |

| <output file="">.vhd (1)</output>                                   | VHDL Variation Wrapper File—Megafunction wrapper file for instantiation in a VHDL design.                            |

| <output file="">.tdf (1)</output>                                   | AHDL Variation Wrapper File—Megafunction wrapper file for instantiation in an AHDL design.                           |

| <output file="">.inc</output>                                       | ADHL Include File—Used in AHDL designs.                                                                              |

| <output file="">.cmp</output>                                       | Component Declaration File—Used in VHDL designs.                                                                     |

| <output file="">.bsf</output>                                       | Block Symbol File—Used in Quartus II Block Design Files (.bdf).                                                      |

| <output file="">_inst.v</output>                                    | Verilog HDL Instantiation Template—Sample Verilog HDL instantiation of the module in the megafunction wrapper file.  |

| <output file="">_inst.vhd</output>                                  | VHDL Instantiation Template—Sample VHDL instantiation of the entity in the megafunction wrapper file.                |

| <output file="">_inst.tdf</output>                                  | Text Design File Instantiation Template—Sample AHDL instantiation of the subdesign in the megafunction wrapper file. |

| Table 6–1. MegaWizard Plug-In Manager Generated Files (Part 2 of 2) |                                                                                                                                                                                                      |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File                                                                | Description                                                                                                                                                                                          |

| <output file="">_bb.v</output>                                      | Black box Verilog HDL Module Declaration—Hollow-body module declaration that can be used in Verilog HDL designs to specify port directions when creating black boxes in third-party synthesis tools. |

| <output file="">_syn.v (2)</output>                                 | Synthesis area and timing estimation netlist—Megafunction netlist used by certain third-party synthesis tools to improve area and timing estimations.                                                |

#### *Notes to Table 6–1:*

- The MegaWizard Plug-In Manager generates either the Verilog HDL, VHDL, or AHDL Variation Wrapper File, depending on the language you select for the output file on the megafunction-selection page of the wizard.

- (2) The MegaWizard Plug-In Manager generates this file only if you turn on the Generate a synthesis area and timing estimation netlist option on the EDA page of the wizard.

#### **Creating a Netlist File for Other Synthesis Tools**

When you use certain megafunctions with third-party EDA synthesis tools (that is, tools other than Quartus II integrated synthesis), you can optionally create a netlist for area and timing estimation instead of a wrapper file.

The netlist file is a representation of the customized logic used in the Quartus II software. The file provides the connectivity of architectural elements in the megafunction but may not represent true functionality. This information enables certain third-party synthesis tools to better report area and timing estimates. In addition, synthesis tools can use the timing information to focus timing-driven optimizations and improve the quality of results.

To generate the netlist, turn on **Generate a synthesis area and timing estimation netlist** on the EDA page of the MegaWizard Plug-In Manager. The netlist file is called *<output file>\_syn.v.* If you use this netlist for synthesis, you must include the megafunction wrapper file *<output file>.v* | vhd in your Quartus II project for placement and routing.

Your synthesis tool may call the Quartus II software in the background to generate this netlist, so you might not be required to perform the extra step of turning on this option.

For information about support for area and timing estimation netlists in your synthesis tool, refer to the tool vendor's documentation or the appropriate chapter in the *Synthesis* section in volume 1 of the *Quartus II Handbook*.

## Instantiating Megafunctions Using the Port and Parameter Definition

You can instantiate the megafunction directly in your Verilog HDL, VHDL, or AHDL code by calling the megafunction and setting its parameters as you would any other module, component, or subdesign.

Refer to the specific megafunction in the Quartus II Help for a list of the megafunction ports and parameters. Quartus II Help also provides a sample VHDL component declaration and AHDL function prototype for each megafunction.

Altera strongly recommends that you use the MegaWizard Plug-In Manager for complex megafunctions such as PLLs, transceivers, and LVDS drivers. For details on using the MegaWizard Plug-In Manager, refer to "Instantiating Megafunctions Using the MegaWizard Plug-In Manager" on page 6–4.

# Inferring Multiplier and DSP Functions from HDL Code

The following sections describe how to infer multiplier and DSP functions from generic HDL code, and, if applicable, how to target the dedicated DSP block architecture in Altera devices:

- "Multipliers—Inferring the lpm\_mult Megafunction from HDL Code" on page 6–7

- "Multiply-Accumulators and Multiply-Adders—Inferring altmult\_accum and altmult\_add Megafunctions from HDL Code" on page 6–10

For synthesis tool features and options, refer to your synthesis tool documentation or the appropriate chapter in the *Synthesis* section in volume 1 of the *Quartus II Handbook*.

## Multipliers—Inferring the Ipm\_mult Megafunction from HDL Code

To infer multiplier functions, synthesis tools look for multipliers and convert them to lpm\_mult or altmult\_add megafunctions, or may map them directly to device atoms. For devices with DSP blocks, the software can implement the function in a DSP block instead of logic,

depending on device utilization. The Quartus II Fitter can also place input and output registers in DSP blocks (that is, perform register packing) to improve performance and area utilization.

For additional information about the DSP block and the supported functions, refer to the appropriate Altera device family handbook and Altera's DSP Solutions Center website.

The following four code samples show Verilog HDL and VHDL examples for unsigned and signed multipliers that synthesis tools can infer as an lpm\_mult or altmult\_add megafunction. Each example fits into one DSP block 9-bit element. In addition, when register packing occurs, no extra logic cells for registers are required.

The signed declaration in Verilog HDL is a feature of the Verilog 2001 Standard.

#### Example 6-1. Verilog HDL Unsigned Multiplier

```

module unsigned_mult (out, a, b);

output [15:0] out;

input [7:0] a;

input [7:0] b;

assign out = a * b;

endmodule

```

#### Example 6–2. Verilog HDL Signed Multiplier with Input and Output Registers (Pipelining = 2)

```

module signed mult (out, clk, a, b);

output [15:0] out;

input clk;

input signed [7:0] a;

input signed [7:0] b;

reg signed [7:0] a_reg;

reg signed [7:0] b reg;

reg signed [15:0] out;

wire signed [15:0] mult out;

assign mult out = a reg * b reg;

always @ (posedge clk)

begin

a reg <= a;

b reg <= b;

out <= mult out;

end

endmodule

```

#### Example 6-3. VHDL Unsigned Multiplier with Input and Output Registers (Pipelining = 2)

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

USE ieee.numeric std.all;

ENTITY unsigned mult IS

PORT (

a: IN UNSIGNED (7 DOWNTO 0);

b: IN UNSIGNED (7 DOWNTO 0);

clk: IN STD LOGIC;

aclr: IN STD LOGIC;

result: OUT UNSIGNED (15 DOWNTO 0)

);

END unsigned mult;

ARCHITECTURE rtl OF unsigned mult IS

SIGNAL a_reg, b_reg: UNSIGNED (7 DOWNTO 0);

BEGIN

PROCESS (clk, aclr)

BEGIN

IF (aclr ='1') THEN

a reg <= (OTHERS => '0');

b reg <= (OTHERS => '0');

result <= (OTHERS => '0');

ELSIF (clk'event AND clk = '1') THEN

a reg <= a;

b reg <= b;

result <= a_reg * b_reg;

END IF;

END PROCESS;

END rtl;

```

#### Example 6-4. VHDL Signed Multiplier

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY signed_mult IS

PORT (

a: IN SIGNED (7 DOWNTO 0);

b: IN SIGNED (7 DOWNTO 0);

result: OUT SIGNED (15 DOWNTO 0)

);

END signed_mult;

BEGIN

result <= a * b;

END rtl;

```

## Multiply-Accumulators and Multiply-Adders—Inferring altmult\_accum and altmult\_add Megafunctions from HDL Code

Synthesis tools detect multiply-accumulators or multiply-adders and convert them to altmult\_accum or altmult\_add megafunctions, respectively, or may map them directly to device atoms. The Quartus II software then places these functions in DSP blocks during placement and routing.

Synthesis tools infer multiply-accumulator and multiply-adder functions only if the Altera device family has dedicated DSP blocks that support these functions.

A multiply-accumulator consists of a multiplier feeding an addition operator. The addition operator feeds a set of registers that then feeds the second input to the addition operator. A multiply-adder consists of two to four multipliers feeding one or two levels of addition, subtraction, or addition/subtraction operators. Addition is always the second-level operator, if it is used. In addition to the multiply-accumulator and multiply-adder, the Quartus II Fitter also places input and output registers into the DSP blocks to pack registers and improve performance and area utilization.

The Verilog HDL and VHDL code samples shown in Examples 6–5 through 6–8 infer specific multiply-accumulators and multiply-adders.

## Example 6–5. Verilog HDL Unsigned Multiply-Accumulator with Input, Output and Pipeline Registers (Latency = 3)

```

module unsig altmult accum (dataout, dataa, datab, clk, aclr, clken);

input [7:0] dataa;

input [7:0] datab;

input clk;

input aclr;

input clken;

output [31:0] dataout;

reg [31:0] dataout;

reg [7:0] dataa_reg;

reg [7:0] datab reg;

reg [15:0] multa_reg;

wire [15:0] multa;

wire [31:0] adder out;

assign multa = dataa_reg * datab_reg;

assign adder_out = multa_reg + dataout;

always @ (posedge clk or posedge aclr)

begin

if (aclr)

begin

dataa_reg <= 8'b0;

datab reg <= 8'b0;

multa reg <= 16'b0;

dataout <= 32'b0;

end

else if (clken)

begin

dataa reg <= dataa;

datab reg <= datab;

multa reg <= multa;

dataout <= adder out;

end

end

endmodule

```

#### Example 6-6. Verilog HDL Signed Multiply-Adder (Latency = 0)

```

module sig_altmult_add (dataa, datab, datac, datad, result);

input signed [15:0] dataa;

input signed [15:0] datab;

input signed [15:0] datac;

input signed [15:0] datad;

output [32:0] result;

wire signed [31:0] mult0_result;

wire signed [31:0] mult1_result;

assign mult0_result = dataa * datab;

assign mult1_result = datac * datad;

assign result = (mult0_result + mult1_result);

endmodule

```

#### Example 6-7. VHDL Unsigned Multiply-Adder with Input, Output and Pipeline Registers (Latency = 3)

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

USE ieee.numeric std.all;

ENTITY unsignedmult add IS

PORT (

a: IN UNSIGNED (7 DOWNTO 0);

b: IN UNSIGNED (7 DOWNTO 0);

c: IN UNSIGNED (7 DOWNTO 0);

d: IN UNSIGNED (7 DOWNTO 0);

clk: IN STD LOGIC;

aclr: IN STD LOGIC;

result: OUT UNSIGNED (15 DOWNTO 0)

);

END unsignedmult add;

ARCHITECTURE rtl OF unsignedmult add IS

SIGNAL a_reg, b_reg, c_reg, d_reg: UNSIGNED (7 DOWNTO 0);

SIGNAL pdt reg, pdt2 reg: UNSIGNED (15 DOWNTO 0);

SIGNAL result reg: UNSIGNED (15 DOWNTO 0);

BEGIN

PROCESS (clk, aclr)

BEGIN

IF (aclr = '1') THEN

a_reg <= (OTHERS => '0');

b reg <= (OTHERS => '0');

c reg <= (OTHERS => '0');

d reg <= (OTHERS => '0');

pdt reg <= (OTHERS => '0');

pdt2_reg <= (OTHERS => '0');

ELSIF (clk'event AND clk = '1') THEN

a reg <= a;

b_reg <= b;

c reg <= c;

d reg <= d;

pdt reg <= a reg * b reg;

pdt2 reg <= c reg * d reg;

result_reg <= pdt_reg + pdt2_reg;

END IF;

END PROCESS;

result <= result_reg;

END rtl;

```

#### Example 6–8. VHDL Signed Multiply-Accumulator with Input, Output and Pipeline Registers (Latency = 3)

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

USE ieee.numeric std.all;

ENTITY sig altmult accum IS

PORT (

a: IN SIGNED (7 DOWNTO 0);

b: IN SIGNED (7 DOWNTO 0);

clk: IN STD LOGIC;

accum out: OUT SIGNED (15 DOWNTO 0)

) ;

END sig_altmult_accum;

ARCHITECTURE rtl OF sig altmult accum IS

SIGNAL a reg, b reg: SIGNED (7 DOWNTO 0);

SIGNAL pdt reg: SIGNED (15 DOWNTO 0);

SIGNAL adder out: SIGNED (15 DOWNTO 0);

BEGIN

PROCESS (clk)

BEGIN

IF (clk'event and clk = '1') THEN

a_reg <= (a);

b reg <= (b);

pdt reg <= a reg * b reg;

adder out <= adder out + pdt reg;

END IF;

END process;

accum out <= adder out;

END rtl;

```

#### Inferring Memory Functions from HDL Code

The following sections describe how to infer memory functions from generic HDL code and, if applicable, to target the dedicated memory architecture in Altera devices:

- "RAM Functions—Inferring altsyncram and altdpram Megafunctions from HDL Code" on page 6–14

- "ROM Functions—Inferring altsyncram and lpm\_rom Megafunctions from HDL Code" on page 6–31

- "Shift Registers—Inferring the altshift\_taps Megafunction from HDL Code" on page 6–36

For synthesis tool features and options, refer to your synthesis tool documentation or the appropriate chapter in the *Synthesis* section in volume 1 of the *Quartus II Handbook*.

Altera's dedicated memory architecture offers a number of advanced features that can be easily targeted using the MegaWizard Plug-In Manager as described in "Instantiating Altera Megafunctions in HDL Code" on page 6–4. The coding recommendations in the following

sections provide portable examples of generic HDL code that infer the appropriate megafunction. However, if you want to use some of the advanced memory features in Altera devices, consider using the megafunction directly so that you can control the ports and parameters more easily.

## RAM Functions—Inferring altsyncram and altdpram Megafunctions from HDL Code

To infer RAM functions, synthesis tools detect sets of registers and logic that can be replaced with the ALTSYNCRAM or ALTDPRAM megafunctions for device families that have dedicated RAM blocks, or may map them directly to device memory atoms. Tools typically consider all signals and variables that have a two-dimensional array type and then create a RAM block, if applicable, based on the way the signals, variables, or both are assigned, referenced, or both in the HDL source description. This section provides examples that demonstrate the coding styles that are inferred to create a memory block.

Standard synthesis tools recognize single-port and simple dual-port (one read port and one write port) RAM blocks. Some tools (such as the Quartus II software) also recognize true dual-port RAM blocks that map to the memory blocks in certain Altera devices. Tools usually do not infer small RAM blocks because small RAM blocks typically can be implemented more efficiently using the registers in regular logic.

If you are using Quartus II integrated synthesis, you can direct the software to infer ROM blocks for all sizes with the **Allow Any RAM Size for Recognition** option under **More Settings** on the **Analysis & Synthesis Settings** page of the **Settings** dialog box.

If your design contains a RAM block that your synthesis tool does not recognize and infer, the design might require a large amount of system memory that potentially can cause compilation problems.

Some synthesis tools provide options to control the implementation of inferred RAM blocks for Altera devices with TriMatrix™ memory blocks. For example, Quartus II integrated synthesis provides the ramstyle synthesis attribute to specify the type of memory block or to specify the use of regular logic instead of a dedicated memory block. Quartus II integrated synthesis does not map inferred memory into Stratix® III MLABs unless the HDL code specifies the appropriate ramstyle attribute, although the Fitter may map some memories to MLABs.

For details about using the ramstyle attribute, refer to the *Quartus II Integrated Synthesis* chapter in volume 1 of the *Quartus II Handbook*. For information about synthesis attributes in other synthesis tools, refer to the appropriate chapter in the *Synthesis* section in volume 1 of the *Quartus II Handbook*.

When you are using a formal verification flow, Altera recommends that you create RAM blocks in separate entities or modules that contain only the RAM logic. In certain formal verification flows, for example, when using Quartus II integrated synthesis, the entity or module containing the inferred RAM is put into a black box automatically because formal verification tools do not support RAM blocks. The Quartus II software issues a warning message when this occurs. If the entity or module contains any additional logic outside the RAM block, this logic also must be treated as a black box for formal verification and therefore cannot be verified.

The following subsections present several guidelines for inferring RAM functions that match the dedicated memory architecture in Altera devices, and then provides recommended HDL code for different types of memory logic.

#### Use Synchronous Memory Blocks

Altera recommends using synchronous memory blocks for Altera designs. The TriMatrix memory blocks in Altera's newest devices are synchronous, so RAM designs that are targeted towards architectures that contain these dedicated memory blocks must be synchronous to be mapped directly into the device architecture. For these devices, asynchronous memory logic is implemented in regular logic cells.

Synchronous memories are supported in all Altera device families. A memory block is considered synchronous if it uses one of the following read behaviors:

- Memory read occurs in a Verilog always block with a clock signal or a VHDL clocked process.

- Memory read occurs outside a clocked block, but there is a synchronous read address (that is, the address used in the read statement is registered). This type of logic is not always inferred as a memory block, depending on the target device architecture.

The synchronous memory structures in Altera devices differ from the structures in other vendors' devices. Match your design to the target device architecture to achieve the best results.

Later subsections provide coding recommendations for various memory types. All of these examples are synchronous to ensure that they can be directly mapped into the dedicated memory architecture available in Altera FPGAs.

For additional information about the dedicated memory blocks in your specific device, refer to the appropriate Altera device family data sheet on the Altera website at www.altera.com.

#### Avoid Unsupported Reset and Control Conditions

To ensure that your HDL code can be implemented in the target device architecture, avoid unsupported reset conditions or other control logic that does not exist in the device architecture.

The RAM contents of Altera memory blocks cannot be cleared with a reset signal during device operation. If your HDL code describes a RAM with a reset signal for the RAM contents, the logic is implemented in regular logic cells instead of a memory block. As a general rule, avoid putting RAM read or write operations in an always block or process block with a reset signal. If you want to specify memory contents, initialize the memory as described in "Specifying Initial Memory Contents at Power-Up" on page 6–29 or write the data to the RAM during device operation.

Example 6–9 shows an example of undesirable code where there is a reset signal that clears part of the RAM contents. Avoid this coding style because it is not supported in Altera memories.

#### Example 6-9. Verilog RAM with Reset Signal that Clears RAM Contents: Not Supported in Device Architecture

```

module clear_ram

input clock,

input reset,

input we,

input [7:0] data in,

input [4:0] address,

output reg [7:0] data out

);

reg [7:0] mem [0:31];

integer i;

always @ (posedge clock or posedge reset)

begin

if (reset == 1'b1)

mem[address] <= 0;</pre>

else if (we == 1'b1)

mem[address] <= data in;</pre>

data out <= mem[address];

end

endmodule

```

Example 6–10 shows an example of undesirable code where the reset signal affects the RAM, although the effect may not be intended. Avoid this coding style because it is not supported in Altera memories.

#### Example 6-10. Verilog RAM with Reset Signal that Affects RAM: Not Supported in Device Architecture

```

module bad reset

input clock,

input reset,

input we,

input [7:0] data in,

input [4:0] address,

output reg [7:0] data out,

input d,

output reg q

);

reg [7:0] mem [0:31];

integer i;

always @ (posedge clock or posedge reset)

begin

if (reset == 1'b1)

q \ll 0;

else

begin

if (we == 1'b1)

mem[address] <= data in;</pre>

data out <= mem[address];</pre>

q \ll d;

end

end

endmodule

```

In addition to reset signals, other control logic can prevent memory logic from being inferred as a memory block. For example, you cannot use a clock enable on the read address registers in Stratix devices, because doing so affects the output latch of the RAM, and therefore the synthesized result in the device RAM architecture would not match the HDL description. In Stratix II, Cyclone<sup>®</sup> II, Arria<sup>™</sup> GX, and other newer devices, however, you can use the address stall feature as a read address clock enable, so there is no such limitation. Check the documentation on your device architecture to ensure that your code matches the hardware available in the device.

#### Check Read-During-Write Behavior

It is important to check the read-during-write behavior of the memory block described in your HDL design as compared to the behavior in your target device architecture. Your HDL source code specifies the memory behavior when you read and write from the same memory address in the same clock cycle. The code specifies that the read returns either the old data at the address, or the new data being written to the address. This is referred to as the read-during-write behavior of the memory block. Altera memory blocks have different read-during-write behavior depending on the target device family, memory mode, and block type.

Synthesis tools map an HDL design into the target device architecture, with the goal of maintaining the functionality described in your source code. Therefore, if your source code specifies unsupported read-during-write behavior for the device RAM blocks, the software must implement the logic outside the RAM hardware in regular logic cells.

One common problem occurs when there is a continuous read in the HDL code, as shown in the following samples. You should avoid using these coding styles.

```

//Verilog HDL concurrent signal assignment

assign q = ram[raddr_reg];

-- VHDL concurrent signal assignment

q <= ram(raddr reg);</pre>

```

When a write operation occurs, this type of HDL implies that the read should immediately reflect the new data at the address, independent of the read clock. However, that is not the behavior of TriMatrix memory blocks. In the device architecture, the new data is not available until the next edge of the read clock. Therefore, if the synthesis tool mapped the logic directly to a TriMatrix memory block, the device functionality and gate-level simulation results would not match the HDL description or function simulation results. If the write clock and read clock are the same, the synthesis tool can infer memory blocks and add extra bypass logic so that the device behavior does match the HDL behavior. If the write and read clocks are different, the synthesis tool cannot reliably add bypass logic, so the logic is implemented in regular logic cells instead of dedicated RAM blocks. The examples in the following sections discuss some of these differences for read-during-write conditions.

In many synthesis tools, you can specify that the read-during-write behavior is not important to your design; for example, if you never read from the same address to which you write in the same clock cycle. For Quartus II integrated synthesis, add the synthesis attribute ramstyle="no\_rw\_check" to allow the software to choose the read-during-write behavior of a RAM, rather than use the behavior specified by your HDL code. Using this type of attribute prevents the synthesis tool from using extra logic to implement the memory block, and in some cases, can allow memory inference when it would otherwise be impossible.

For more information about attribute syntax, the no\_rw\_check attribute value, or specific options for your synthesis tool, refer to your synthesis tool documentation or to the appropriate chapter in the *Synthesis* section in volume 1 of the *Quartus II Handbook*.

The following subsections provide coding recommendations for various memory types. Each example describes the read-during-write behavior and addresses the support for the memory type in Altera devices.

Single-Clock Synchronous RAM with Old Data Read-During-Write Behavior

The code examples in this section show Verilog HDL and VHDL code that infers simple dual-port, single-clock synchronous RAM. Single-port RAM blocks use a similar coding style.

The read-during-write behavior in these examples is to read the old data at the memory address. Refer to "Check Read-During-Write Behavior" on page 6–17 for details. Altera recommends that you use this coding style as long as your design does not require that a simultaneous read and write to the same RAM location read the new value that is currently being written to that RAM location.

If you require that the read-during-write results in new data, refer to "Single-Clock Synchronous RAM with New Data Read-During-Write Behavior" on page 6–21.

The simple dual-port RAM code samples shown in Examples 6–11 and 6–12 map directly into Altera TriMatrix memory.

Single-port versions of memory blocks (that is, using the same read address and write address signals) can allow better RAM utilization than dual-port memory blocks, depending on the device family.

#### Example 6–11. Verilog HDL Single-Clock Simple Dual-Port Synchronous RAM with Old Data Read-During-Write Behavior

```

module single_clk_ram(

output reg [7:0] q,

input [7:0] d,

input [6:0] write_address, read_address,

input we, clk

);

reg [7:0] mem [127:0];

always @ (posedge clk) begin

if (we)

mem[write_address] <= d;

q <= mem[read_address]; // q doesn't get d in this clock cycle end

endmodule</pre>

```

### Example 6–12. VHDL Single-Clock Simple Dual-Port Synchronous RAM with Old Data Read-During-Write Behavior

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY single clock ram IS

PORT (

clock: IN STD LOGIC;

data: IN STD LOGIC VECTOR (2 DOWNTO 0);

write address: IN INTEGER RANGE 0 to 31;

read address: IN INTEGER RANGE 0 to 31;

we: IN STD LOGIC;

q: OUT STD LOGIC VECTOR (2 DOWNTO 0)

);

END single_clock_ram;

ARCHITECTURE rtl OF single clock ram IS

TYPE MEM IS ARRAY(0 TO 31) OF STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL ram block: MEM;

BEGIN

PROCESS (clock)

BEGIN

IF (clock'event AND clock = '1') THEN

IF (we = '1') THEN

ram_block(write_address) <= data;</pre>

END IF;

q <= ram block(read address);</pre>

-- VHDL semantics imply that q doesn't get data

-- in this clock cycle

END IF;

END PROCESS;

END rtl;

```

Single-Clock Synchronous RAM with New Data Read-During-Write Behavior

These examples describe RAM blocks in which a simultaneous read and write to the same location reads the new value that is currently being written to that RAM location.

To implement this behavior in the target device, synthesis software adds bypass logic around the RAM block. This bypass logic increases the area utilization of the design and decreases the performance if the RAM block is part of the design's critical path. Refer to "Check Read-During-Write Behavior" on page 6–17 for details. If this behavior is not required for your design, use the examples from "Single-Clock Synchronous RAM with Old Data Read-During-Write Behavior" on page 6–19.

The simple dual-port RAM examples shown in Examples 6–13 and 6–14 require bypass the software to create this logic around the RAM block.

Single-port versions of the Verilog memory block (that is, using the same read address and write address signals) do not require any logic cells to create bypass logic in Arria GX devices, and Stratix and Cyclone series of devices, because the device memory supports new data read-during-write behavior when in single-port mode (same clock, same read and write address).

## Example 6–13. Verilog HDL Single-Clock Simple Dual-Port Synchronous RAM with New Data Read-During-Write Behavior

```

module single_clock_wr_ram(

output reg [7:0] q,

input [7:0] d,

input [6:0] write_address, read_address,

input we, clk

);

reg [7:0] mem [127:0];

always @ (posedge clk) begin

if (we)

mem[write_address] = d;

q = mem[read_address]; // q does get d in this clock cycle if we is high end

endmodule

```

Note that Example 6–13 is similar to Example 6–11, but Example 6–13 uses a blocking assignment for the write so that the data is assigned immediately.

An alternative way to create a single-clock RAM is to use an assign statement to read the address of mem to create the output q, as shown in the following coding style. By itself, the code describes new data read-during-write behavior. However, if the RAM output feeds a register in another hierarchy, then a read-during-write would result in the old data. Synthesis tools may not infer a RAM block if the tool cannot determine which behavior is described, such as when the memory feeds a hard hierarchical partition boundary. For this reason, avoid using this alternate type of coding style.

```

reg [7:0] mem [127:0];

reg [6:0] read_address_reg;

always @ (posedge clk) begin

if (we)

mem[write_address] <= d;

read_address_reg <= read_address;

end

assign q = mem[read address reg];</pre>

```

The following VHDL sample (Example 6–14) uses a concurrent signal assignment to read from the RAM. By itself, this example describes new data read-during-write behavior. However, if the RAM output feeds a register in another hierarchy, then a read-during-write would result in the old data. Synthesis tools may not infer a RAM block if the tool cannot determine which behavior is described, such as when the memory feeds a hard hierarchical partition boundary.

## Example 6–14. VHDL Single-Clock Simple Dual-Port Synchronous RAM with New Data Read-During-Write Behavior

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY single clock rw ram IS

PORT (

clock: IN STD LOGIC;

data: IN STD LOGIC VECTOR (2 DOWNTO 0);

write address: IN INTEGER RANGE 0 to 31;

read address: IN INTEGER RANGE 0 to 31;

we: IN STD LOGIC;

q: OUT STD_LOGIC_VECTOR (2 DOWNTO 0)

);

END single clock rw ram;

ARCHITECTURE rtl OF single_clock_rw_ram IS

TYPE MEM IS ARRAY(0 TO 31) OF STD LOGIC VECTOR(2 DOWNTO 0);

SIGNAL ram block: MEM;

SIGNAL read address reg: INTEGER RANGE 0 to 31;

PROCESS (clock)

BEGIN

IF (clock'event AND clock = '1') THEN

IF (we = '1') THEN

ram block(write address) <= data;

read address reg <= read address;

END IF;

END PROCESS;

q <= ram_block(read_address_reg);</pre>

END rtl;

```

This example does not infer a RAM block for the APEX series of devices, ACEX®, or the FLEX® series of devices by default because the read-during-write behavior depends on surrounding logic. For Quartus II integrated synthesis, if you do not require the read-through-write capability, add the synthesis attribute ramstyle="no\_rw\_check" to allow the software to choose the read-during-write behavior of a RAM, rather than use the behavior specified by your HDL code.

#### Simple Dual-Port, Dual-Clock Synchronous RAM

In dual clock designs, synthesis tools cannot accurately infer the read-during-write behavior because it depends on the timing of the two clocks within the target device. Therefore, the read-during-write behavior of the synthesized design is undefined and may differ from your original HDL code. Refer to "Check Read-During-Write Behavior" on page 6–17 for details.

When Quartus II integrated synthesis infers this type of RAM, it issues a warning because of the undefined read-during-write behavior. If this functionality is acceptable in your design, you can avoid the warning by adding the synthesis attribute ramstyle="no\_rw\_check" to allow the software to choose the read-during-write behavior of a RAM.

The code samples shown in Examples 6–15 and 6–16 show Verilog HDL and VHDL code that infers dual-clock synchronous RAM. The exact behavior depends on the relationship between the clocks.

#### Example 6-15. Verilog HDL Simple Dual-Port, Dual-Clock Synchronous RAM

```

module dual clock ram(

output reg [7:0] q,

input [7:0] d,

input [6:0] write address, read address,

input we, clk1, clk2

);

reg [6:0] read address reg;

reg [7:0] mem [127:0];

always @ (posedge clk1)

begin

if (we)

mem[write address] <= d;</pre>

end

always @ (posedge clk2) begin

q <= mem[read_address_reg];</pre>

read address reg <= read address;

end

endmodule

```

#### Example 6-16. VHDL Simple Dual-Port, Dual-Clock Synchronous RAM

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY dual clock ram IS

PORT (

clock1, clock2: IN STD LOGIC;

data: IN STD LOGIC VECTOR (3 DOWNTO 0);

write address: IN INTEGER RANGE 0 to 31;

read address: IN INTEGER RANGE 0 to 31;

we: IN STD LOGIC;

q: OUT STD LOGIC VECTOR (3 DOWNTO 0)

);

END dual clock ram;

ARCHITECTURE rtl OF dual clock ram IS

TYPE MEM IS ARRAY (0 TO 31) OF STD LOGIC VECTOR (3 DOWNTO 0);

SIGNAL ram block: MEM;

SIGNAL read address reg : INTEGER RANGE 0 to 31;

BEGIN

PROCESS (clock1)

IF (clock1'event AND clock1 = '1') THEN

```

#### True Dual-Port Synchronous RAM

The code examples in this section show Verilog HDL and VHDL code that infers true dual-port synchronous RAM. Different synthesis tools may differ in their support for these types of memories. This section describes the inference rules for Quartus II integrated synthesis. This type of RAM inference is supported only for Arria GX devices, and the Stratix and Cyclone series of devices.

Altera TriMatrix memory blocks have two independent address ports, allowing for operations on two unique addresses simultaneously. A read operation and a write operation can share the same port if they share the same address. The Quartus II software infers true dual-port RAMs in Verilog HDL and VHDL with any combination of independent read or write operations in the same clock cycle, with at most two unique port addresses, performing two reads and one write, two writes and one read, or two writes and two reads in one clock cycle with one or two unique addresses.

In the TriMatrix RAM block architecture, there is no priority between the two ports. Therefore, if you write to the same location on both ports at the same time, the result is indeterminate in the device architecture. You must ensure your HDL code does not imply priority for writes to the memory block, if you want the design to be implemented in a dedicated hardware memory block. For example, if both ports are defined in the same process block, the code is synthesized and simulated sequentially so there would be a priority between the two ports. If your code does imply a priority, the logic cannot be implemented in the device RAM blocks and is implemented in regular logic cells.

You must also consider the read-during-write behavior of the RAM block, to ensure that it can be mapped directly to the device RAM architecture. Refer to "Check Read-During-Write Behavior" on page 6–17 for details.

When a read and write operation occur on the same port for the same address, the read operation may behave as follows:

- Read new data. This mode matches the behavior of TriMatrix memory blocks.

- Read old data. This mode is supported only by Stratix IV, Stratix III, and Cyclone III TriMatrix memory blocks. This behavior is not possible in TriMatrix memory blocks of other families.

When a read and write operation occur on different ports for the same address (also known as mixed port), the read operation may behave as follows:

- **Read new data.** Quartus II integrated synthesis supports this mode by creating bypass logic around the TriMatrix memory block.

- Read old data. This behavior is supported by TriMatrix memory blocks.

The Verilog HDL single-clock code sample shown in Example 6–17 maps directly into Altera TriMatrix memory. When a read and write operation occur on the same port for the same address, the new data being written to the memory is read. When a read and write operation occur on different ports for the same address, the old data in the memory is read. Simultaneous writes to the same location on both ports results in indeterminate behavior.

A dual-clock version of this design describes the same behavior, but the memory in the target device will have undefined mixed port read-during-write behavior because it depends on the relationship between the clocks.

#### Example 6-17. Verilog HDL True Dual-Port RAM with Single Clock

```

module true dual port ram single clock

input [(DATA WIDTH-1):0] data a, data b,

input [(ADDR WIDTH-1):0] addr a, addr b,

input we a, we b, clk,

output reg [(DATA_WIDTH-1):0] q_a, q_b

);

parameter DATA WIDTH = 8;

parameter ADDR WIDTH = 6;

// Declare the RAM variable

reg [DATA WIDTH-1:0] ram[2**ADDR WIDTH-1:0];

always @ (posedge clk)

begin // Port A

if (we a)

ram[addr a] <= data a;</pre>

q a <= data a;

end

```

If you use the Verilog HDL read statements shown below instead of the if-else statements in Example 6–17, the HDL code specifies that the read results in old data when a read and write operation occur at the same time for the same address on the same port or mixed ports. This behavior is supported only in the TriMatrix memories of Stratix IV, Stratix III and Cyclone III devices, and is not inferred as memory for other device families.

```

always @ (posedge clk)

begin // Port A

if (we_a)

ram[addr_a] <= data_a;

q_a <= ram[addr_a];

end

always @ (posedge clk)

begin // Port B

if (we_b)

ram[addr_b] <= data_b;

q_b <= ram[addr_b];

end</pre>

```

The VHDL single-clock code sample shown in Example 6–18 maps directly into Altera TriMatrix memory. When a read and write operation occur on the same port for the same address, the new data being written to the memory is read. When a read and write operation occur on different ports for the same address, the old data in the memory is read. Because simultaneous writes to the same location on both ports results in indeterminate behavior, Altera recommends that you avoid this condition.

A dual-clock version of this design describes the same behavior, but the memory in the target device will have undefined mixed port read-during-write behavior because it depends on the relationship between the clocks.

#### Example 6–18. VHDL True Dual-Port RAM with Single Clock

```

library ieee;

use ieee.std logic 1164.all;

entity true_dual_port_ram_single_clock is

generic

DATA WIDTH : natural := 8;

ADDR WIDTH : natural := 6

);

port

clk : in std logic;

addr a: in natural range 0 to 2**ADDR WIDTH - 1;

addr_b: in natural range 0 to 2**ADDR_WIDTH - 1;

data a: in std logic vector((DATA WIDTH-1) downto 0);

data b: in std logic vector((DATA WIDTH-1) downto 0);

we a: in std logic := '1';

we_b: in std_logic := '1';

q a : out std logic vector((DATA WIDTH -1) downto 0);

q_b : out std_logic_vector((DATA_WIDTH -1) downto 0)

);

end true dual port ram single clock;

architecture rtl of true_dual_port_ram_single_clock is

-- Build a 2-D array type for the RAM

subtype word_t is std_logic_vector((DATA_WIDTH-1) downto 0);

type memory t is addr a (raddr'high downto 0) of word t;

-- Declare the RAM signal.

signal ram : memory_t;

begin

process(clk)

begin

if (rising edge(clk)) then -- Port A

if (we a = '1') then

ram(addr a) <= data a;</pre>

-- Read-during-write on the same port returns NEW data

q_a <= data_a;

else

-- Read-during-write on the mixed port returns OLD data

q_a <= ram(addr_a);</pre>

end if;

end if:

end process;

process(clk)

begin

if(rising_edge(clk)) then -- Port B

if (we b = '1') then

ram(addr b) <= data b;</pre>

```

```

-- Read-during-write on the same port returns NEW data

q_b <= data_b;

else

-- Read-during-write on the mixed port returns OLD data

q_b <= ram(addr_b);

end if;

end if;

end process;

end rtl:

```

#### Specifying Initial Memory Contents at Power-Up

Your synthesis tool may offer various ways to specify the initial contents of an inferred memory.

Certain device memory types do not support initialized memory, such as the M-RAM blocks in Stratix and Stratix II devices.

There are slight power-up and initialization differences between dedicated RAM blocks and the Stratix III MLAB memory due to the continuous read of the MLAB. Altera dedicated RAM block outputs always power-up to zero and are set to the initial value on the first read. For example, if address 0 is pre-initialized to FF, the RAM block powers up with the output at 0. A subsequent read after power up from address 0 outputs the pre-initialized value of FF. Therefore, if a RAM is powered up and an enable (read enable or clock enable) is held low, then the power-up output of 0 is maintained until the first valid read cycle. The Stratix III MLAB is implemented using registers that power-up to 0, but are initialized to their initial value immediately at power-up or reset. You will therefore see the initial value regardless of the enable status. Quartus II integrated synthesis does not map inferred memory to MLABs unless the HDL code specifies the appropriate ramstyle attribute.

Quartus II integrated synthesis supports the ram\_init\_file synthesis attribute that allows you to specify a Memory Initialization File (.mif) for an inferred RAM block.

For information about the ram\_init\_file attribute, refer to the *Quartus II Integrated Synthesis* chapter in volume 1 of the *Quartus II Handbook*. For information about synthesis attributes in other synthesis tools, refer to the tool vendor's documentation.

In Verilog HDL, you can use an initial block to initialize the contents of an inferred memory. Quartus II integrated synthesis automatically converts the initial block into a MIF for the inferred RAM. Example 6–19 shows Verilog HDL code that infers a simple dual-port RAM block and corresponding MIF file.

#### Example 6–19. Verilog HDL RAM with Initialized Contents

```

module ram with init(

output reg [7:0] q,

input [7:0] d,

input [4:0] write address, read address,

input we, clk

);

reg [7:0] mem [0:31];

integer i;

initial begin

for (i = 0; i < 32; i = i + 1)

mem[i] = i[7:0];

end

always @ (posedge clk) begin

if (we)

mem[write address] <= d;</pre>

q <= mem[read address];</pre>

end

endmodule

```

Quartus II integrated synthesis and other synthesis tools also support the \$readmemb and \$readmemb commands so that RAM and ROM initialization work identically in synthesis and simulation. Example 6–20 shows an initial block that initializes an inferred RAM block using the \$readmemb command.

Refer to the Verilog Language Reference Manual (LRM) 1364-2001 Section 17.2.8 for details about the format of the **ram.txt** file.

#### Example 6-20. Verilog HDL RAM Initialized with the readmemb Command

```

reg [7:0] ram[0:15];

initial

begin

$readmemb("ram.txt", ram);

end

```

In VHDL, you can initialize the contents of an inferred memory by specifying a default value for the corresponding signal. Quartus II integrated synthesis automatically converts the default value into a MIF for the inferred RAM. Example 6–21 shows VHDL code that infers a simple dual-port RAM block and corresponding MIF file.

#### Example 6-21. VHDL RAM with Initialized Contents

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

use ieee.numeric std.all;

ENTITY ram with init IS

PORT (

clock: IN STD LOGIC;

data: IN UNSIGNED (7 DOWNTO 0);

write address: IN integer RANGE 0 to 31;

read address: IN integer RANGE 0 to 31;

we: IN std logic;

q: OUT UNSIGNED (7 DOWNTO 0));

END;

ARCHITECTURE rtl OF ram with init IS

TYPE MEM IS ARRAY(31 DOWNTO 0) OF unsigned(7 DOWNTO 0);

FUNCTION initialize ram

return MEM is

variable result : MEM;

BEGIN

FOR i IN 31 DOWNTO 0 LOOP

result(i) := to unsigned(natural(i), natural'(8));

END LOOP;

RETURN result;

END initialize ram;

SIGNAL ram block : MEM := initialize ram;

BEGIN

PROCESS (clock)

BEGIN

IF (clock'event AND clock = '1') THEN

IF (we = '1') THEN

ram block(write address) <= data;</pre>

END IF;

q <= ram_block(read_address);</pre>

END IF;

END PROCESS;

END rtl;

```

## ROM Functions—Inferring altsyncram and lpm\_rom Megafunctions from HDL Code

To infer ROM functions, synthesis tools detect sets of registers and logic that can be replaced with the altsyncram or lpm\_rom megafunctions, depending on the target device family, only for device families that have dedicated memory blocks.

ROMs are inferred when a CASE statement exists in which a value is set to a constant for every choice in the case statement. Because small ROMs typically achieve the best performance when they are implemented using the registers in regular logic, each ROM function must meet a minimum size requirement to be inferred and placed into memory.

If you are using Quartus II integrated synthesis, you can direct the software to infer ROM blocks for all sizes with the **Allow Any ROM Size for Recognition** option under **More Settings** on the **Analysis & Synthesis Settings** page of the **Settings** dialog box.

Some synthesis tools provide options to control the implementation of inferred ROM blocks for Altera devices with TriMatrix memory blocks. For example, Quartus II integrated synthesis provides the romstyle synthesis attribute to specify the type of memory block or to specify the use of regular logic instead of a dedicated memory block.

For details about using the romstyle attribute, refer to the *Quartus II Integrated Synthesis* chapter in volume 1 of the *Quartus II Handbook*. For information about synthesis attributes in other synthesis tools, refer to the appropriate chapter in the *Synthesis* section in volume 1 of the *Quartus II Handbook*.

When you are using a formal verification flow, Altera recommends that you create ROM blocks in separate entities or modules that contain only the ROM logic because you may need to treat the entity and module as a black box during formal verification.

Because formal verification tools do not support ROM megafunctions, Quartus II integrated synthesis does not infer ROM megafunctions when a formal verification tool is selected.

The Verilog HDL and VHDL code samples shown in Examples 6–22, 6–23, 6–24, and 6–25 infer synchronous ROM blocks. Depending on the device family's dedicated RAM architecture, the ROM logic may have to be synchronous; consult the device family handbook for details.

For device architectures with synchronous RAM blocks, such as the Stratix series devices and newer device families, either the address or the output has to be registered for ROM code to be inferred. When output registers are used, the registers are implemented using the input registers of the RAM block, but the functionality of the ROM is not changed. If you register the address, the power-up state of the inferred ROM can be different from the HDL design. In this scenario, the synthesis software issues a warning. The Quartus II Help explains the condition under which the functionality changes when you are using Quartus II integrated synthesis.

These ROM code samples map directly to the Altera TriMatrix memory architecture.

#### Example 6-22. Verilog HDL Synchronous ROM

```

module sync_rom (clock, address, data_out);

input clock;

input [7:0] address;

output [5:0] data_out;

reg [5:0] data_out;

always @ (posedge clock)

begin

case (address)

8'b000000000: data_out = 6'b101111;

8'b00000001: data_out = 6'b110110;

...

8'b11111110: data_out = 6'b000001;

8'b11111111: data_out = 6'b101010;

endcase

end

endmodule

```

#### Example 6-23. VHDL Synchronous ROM

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY sync rom IS

PORT (

clock: IN STD LOGIC;

address: IN STD LOGIC VECTOR (7 downto 0);

data out: OUT STD LOGIC VECTOR(5 downto 0)

);

END sync rom;

ARCHITECTURE rtl OF sync rom IS

PROCESS (clock)

BEGIN

IF rising edge (clock) THEN

CASE address IS

WHEN "00000000" => data out <= "101111";

WHEN "00000001" => data out <= "110110";

WHEN "11111110" => data out <= "000001";

WHEN "11111111" => data out <= "101010";

WHEN OTHERS => data out <= "101111";

END CASE;

END IF:

END PROCESS;

END rtl;

```

#### Example 6-24. Verilog HDL Dual-Port Synchronous ROM Using readmemb

```

module dual port rom (

input [(addr width-1):0] addr a, addr b,

input clk,

output reg [(data width-1):0] q a, q b

);

parameter data_width = 8;

parameter addr width = 8;

reg [data width-1:0] rom[2**addr width-1:0];

initial // Read the memory contents in the file dual port rom init.txt.

begin

$readmemb("dual port rom init.txt", rom);

end

always @ (posedge clk)

begin

q_a <= rom[addr_a];</pre>

q b <= rom[addr b];

end

endmodule

```

#### Example 6-25. VHDL Dual-Port Synchronous ROM Using Initialization Function

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity dual_port_rom is

generic (

DATA_WIDTH : natural := 8;

ADDR WIDTH : natural := 6

);

port (

: in std logic;

addr a: in natural range 0 to 2**ADDR WIDTH - 1;

addr b: in natural range 0 to 2**ADDR WIDTH - 1;

: out std logic vector((DATA WIDTH -1) downto 0);

q a

: out std logic vector((DATA WIDTH -1) downto 0)

q b

end entity;

architecture rtl of dual port rom is

-- Build a 2-D array type for the ROM

subtype word t is std logic vector((DATA WIDTH-1) downto 0);

type memory t is array(addr a'high downto 0) of word t;

function init rom

return memory t is

variable tmp : memory t := (others => '0'));

begin

for addr pos in 0 to 2**ADDR WIDTH - 1 loop

-- Initialize each address with the address itself

tmp(addr pos) := std logic vector(to unsigned(addr pos, \ DATA WIDTH));

end loop;

```

```

return tmp;

end init rom;

-- Declare the ROM signal and specify a default initialization value.

signal rom : memory t := init rom;

begin

process(clk)

begin

if (rising edge(clk)) then

q a <= rom(addr a);

q b <= rom(addr b);

end if;

end process;

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity dual port rom is

generic (

DATA WIDTH : natural := 8;

ADDR WIDTH : natural := 6

);

port (

: in std logic;

addr a: in natural range 0 to 2**ADDR WIDTH - 1;

addr b: in natural range 0 to 2**ADDR WIDTH - 1;

: out std logic vector((DATA WIDTH -1) downto 0);

q_b

: out std logic vector((DATA WIDTH -1) downto 0)

);

end entity;

architecture rtl of dual port rom is

-- Build a 2-D array type for the ROM

subtype word t is std logic vector((DATA WIDTH-1) downto 0);

type memory t is array(addr a'high downto 0) of word t;

function init rom

return memory t is

variable tmp : memory t := (others => (others => '0'));

begin

for addr pos in 0 to 2**ADDR WIDTH - 1 loop

-- Initialize each address with the address itself

tmp(addr pos) := std logic vector(to unsigned(addr pos, DATA WIDTH));

end loop;

return tmp;

end init rom;

-- Declare the ROM signal and specify a default initialization value.

signal rom : memory t := init rom;

begin

process(clk)

begin

if (rising edge(clk)) then

q a <= rom(addr a);

q b <= rom(addr b);

end if;

end process;

```

## Shift Registers—Inferring the altshift\_taps Megafunction from HDL Code

To infer shift registers, synthesis tools detect a group of shift registers of the same length and convert them to an ALTSHIFT\_TAPS megafunction. To be detected, all the shift registers must have the following characteristics:

- Use the same clock and clock enable

- Do not have any other secondary signals

- Have equally spaced taps that are at least three registers apart

When you are using a formal verification flow, Altera recommends that you create shift register blocks in separate entities or modules containing only the shift register logic, because you may need to treat the entity or module as a black box during formal verification.

Because formal verification tools do not support shift register megafunctions, the Quartus II integrated synthesis does not infer the ALTSHIFT\_TAPS megafunction when a formal verification tool is selected. You can select EDA tools for use with your Quartus II project on the **EDA Tool Settings** page of the **Settings** dialog box.

For more information about the altshift\_taps megafunction, refer to the altshift\_taps Megafunction User Guide.

Synthesis software recognizes shift registers only for device families that have dedicated RAM blocks and the software uses certain guidelines to determine the best implementation. The following guidelines are followed in Quartus II integrated synthesis and also are generally followed by other EDA tools:

- For FLEX 10K® and ACEX 1K devices, the software does not infer ALTSHIFT\_TAPS megafunctions because FLEX 10K and ACEX 1K devices have a relatively small amount of dedicated memory.

- For APEX 20K and APEX II devices, the software infers the ALTSHIFT\_TAPS megafunction only if the shift register has more than a total of 128 bits. Smaller shift registers typically do not benefit from implementation in dedicated memory.

- For Arria GX devices, and the Stratix and Cyclone series devices, the software determines whether to infer the ALTSHIFT\_TAPS megafunction based on the width of the registered bus (*W*), the length between each tap (*L*), and the number of taps (*N*).

- If the registered bus width is one (W = 1), the software infers ALTSHIFT\_TAPS if the number of taps times the length between each tap is greater than or equal to 64 ( $N \times L \ge 64$ ).

• If the registered bus width is greater than one (W > 1), the software infers ALTSHIFT\_TAPS if the registered bus width times the number of taps times the length between each tap is greater than or equal to  $32 (W \times N \times L \ge 32)$ .

If the length between each tap (L) is not a power of two, the software uses more logic to decode the read and write counters. This situation occurs because for different sizes of shift registers, external decode logic that uses logic elements (LEs) or Adaptive Logic Modules (ALMs) is required to implement the function. This decode logic eliminates the performance and utilization advantages of implementing shift registers in memory.

The registers that the software maps to the ALTSHIFT\_TAPS megafunction and places in RAM are not available in a Verilog HDL or VHDL output file for simulation tools because their node names do not exist after synthesis.

# Simple Shift Register

The code samples shown in Example 6–26 and Example 6–27 show a simple, single-bit wide, 64-bit long shift register. The synthesis software implements the register (W=1 and M=64) in an ALTSHIFT\_TAPS megafunction for supported devices. If the length of the register is less than 64 bits, the software implements the shift register in logic.

# Example 6-26. Verilog HDL Single-Bit Wide, 64-Bit Long Shift Register

```

module shift_lx64 (clk, shift, sr_in, sr_out);

input clk, shift;

input sr_in;

output sr_out;

reg [63:0] sr;

always @ (posedge clk)

begin

if (shift == l'b1)

begin

sr[63:1] <= sr[62:0];

sr[0] <= sr_in;

end

end

assign sr_out = sr[63];

endmodule</pre>

```

#### Example 6–27. VHDL Single-Bit Wide, 64-Bit Long Shift Register

```

LIBRARY IEEE;

USE IEEE.STD LOGIC 1164.all;

ENTITY shift 1x64 IS

PORT (

clk: IN STD LOGIC;

shift: IN STD LOGIC;

sr in: IN STD LOGIC;

sr out: OUT STD LOGIC

);

END shift 1x64;

ARCHITECTURE arch OF shift 1x64 IS

TYPE sr length IS ARRAY (63 DOWNTO 0) OF STD LOGIC;

SIGNAL sr: sr length;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT and clk = '1') THEN

IF (shift = '1') THEN

sr(63 DOWNTO 1) <= sr(62 DOWNTO 0);</pre>

sr(0) <= sr in;</pre>

END IF;

END IF;

END PROCESS;

sr out <= sr(63);

END arch;

```

# Shift Register with Evenly Spaced Taps

The code samples shown in Examples 6–28 and 6–29 show a Verilog HDL and VHDL 8-bit wide, 64-bit long shift register (W > 1 and M = 64) with evenly spaced taps at 15, 31, and 47. The synthesis software implements this function in a single ALTSHIFT\_TAPS megafunction and maps it to RAM in supported devices.

#### Example 6-28. Verilog HDL 8-Bit Wide, 64-Bit Long Shift Register with Evenly Spaced Taps

```

sr[0] <= sr_in;

end

end

assign sr_tap_one = sr[15];

assign sr_tap_two = sr[31];

assign sr_tap_three = sr[47];

assign sr_out = sr[63];

endmodule</pre>

```

#### Example 6-29. VHDL 8-Bit Wide, 64-Bit Long Shift Register with Evenly Spaced Taps

```

LIBRARY IEEE;

USE IEEE.STD LOGIC 1164.all;

ENTITY shift 8x64 taps IS

PORT (

clk: IN STD LOGIC;

shift: IN STD LOGIC;

sr_in: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

sr tap one: OUT STD LOGIC VECTOR(7 DOWNTO 0);

sr tap two : OUT STD LOGIC VECTOR(7 DOWNTO 0);

sr tap three: OUT STD LOGIC VECTOR(7 DOWNTO 0);

sr out: OUT STD LOGIC VECTOR(7 DOWNTO 0)

);

END shift_8x64_taps;

ARCHITECTURE arch OF shift 8x64 taps IS

SUBTYPE sr_width IS STD_LOGIC_VECTOR(7 DOWNTO 0);

TYPE sr length IS ARRAY (63 DOWNTO 0) OF sr width;

SIGNAL sr: sr length;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT and clk = '1') THEN

IF (shift = '1') THEN

sr(63 DOWNTO 1) <= sr(62 DOWNTO 0);</pre>

sr(0) <= sr_in;

END IF;

END IF;

END PROCESS;

sr_tap_one <= sr(15);</pre>

sr_tap_two <= sr(31);</pre>

sr_tap_three <= sr(47);</pre>

sr out <= sr(63);

END arch;

```

# Coding Guidelines for Registers and Latches

This section provides device-specific coding recommendations for Altera registers and latches. Understanding the architecture of the target Altera device helps ensure that your code produces the expected results and achieves the optimal quality of results.

This section provides guidelines in the following areas:

- "Register Power-Up Values in Altera Devices"

- "Secondary Register Control Signals Such as Clear and Clock Enable" on page 6–42

- "Latches" on page 6–46

# Register Power-Up Values in Altera Devices

Registers in the device core always power up to a low (0) logic level on all Altera devices. However, there are ways to implement logic such that registers behave as if they were powering up to a high (1) logic level.

If you use a preset signal on a device that does not support presets in the register architecture, then your synthesis tool may convert the preset signal to a clear signal, which requires synthesis to perform an optimization referred to as NOT gate push-back. NOT gate push-back adds an inverter to the input and the output of the register so that the reset and power-up conditions will appear to be high but the device operates as expected. In this case, your synthesis tool may issue a message informing you about the power-up condition. The register itself powers up low, but the register output is inverted so the signal that arrives at all destinations is high.

Due to these effects, if you specify a non-zero reset value, you may cause your synthesis tool to use the asynchronous clear (aclr) signals available on the registers to implement the high bits with NOT gate push-back. In that case, the registers look as though they power up to the specified reset value. You see this behavior, for example, if your design targets FLEX 10KE or ACEX devices.

When a load signal is available in the device, your synthesis tools can implement a reset of 1 or 0 value by using an asynchronous load of 1 or 0. When the synthesis tool uses an asynchronous load signal, it is not performing NOT gate push-back, so the registers power up to a 0 logic level.

For additional details, refer to the appropriate device family handbook or the appropriate handbook of the Altera website at www.altera.com.

Designers typically use an explicit reset signal for the design, which forces all registers into their appropriate values after reset but not necessarily at power-up. You can create your design such that the asynchronous reset allows the board to operate in a safe condition and then you can bring up the design with the reset active. This is a good practice so you do not depend on the power-up conditions of the device.

You can make the your design more stable and avoid potential glitches by synchronizing external or combinational logic of the device architecture before you drive the asynchronous control ports of registers.

For additional information about good synchronous design practices, refer to the *Design Recommendations for Altera Devices and the Quartus II Design Assistant* chapter in volume 1 of the *Quartus II Handbook*.

If you want to force a particular power-up condition for your design, use the synthesis options available in your synthesis tool. With Quartus II integrated synthesis, you can apply the **Power-Up Level** logic option. You can also apply the option with an altera\_attribute assignment in your source code. Using this option forces synthesis to perform NOT gate push-back because synthesis tools cannot actually change the power-up states of core registers.

You can apply the Quartus II integrated synthesis **Power-Up Level** assignment to a specific register or to a design entity, module or subdesign. If you do so, every register in that block receives the value. Registers power up to 0 by default; therefore you can use this assignment to force all registers to power up to 1 using NOT gate push-back.

Be aware that using NOT gate push-back as a global assignment could slightly degrade the quality of results due to the number of inverters that are needed. In some situations, issues are caused by enable or secondary control logic inference. It may also be more difficult to migrate such a design to an ASIC or a HardCopy® device. You can simulate the power-up behavior in a functional simulation if you use initialization.

The **Power-Up Level** option and the altera\_attribute assignment are described in the *Quartus II Integrated Synthesis* chapter in volume 1 of the *Quartus II Handbook*.

Some synthesis tools can also read the default or initial values for registered signals and implement this behavior in the device. For example, Quartus II integrated synthesis converts default values for registered signals into Power-Up Level settings. That way, the synthesized behavior matches the power-up state of the HDL code during a functional simulation.

For example, the code samples in Example 6–30 and Example 6–31 both infer a register for q and set its power-up level to high (while the reset value is 0).

# Example 6-30. Verilog Register with Reset and High Power-Up Value

```

reg q = 1'b1;

always @ (posedge clk or posedge aclr)

begin

if (aclr)

q <= 1'b0;

else

q <= d;

end</pre>

```

# Example 6-31. VHDL Register with Reset and High Power-Up Level

```

SIGNAL q : STD_LOGIC := '1'; -- q has a default value of '1'

PROCESS (clk, reset)

BEGIN

IF (reset = '1') THEN

q <= '0';

ELSIF (rising_edge(clk)) THEN

q <= d;

END IF;

END PROCESS;</pre>

```

# Secondary Register Control Signals Such as Clear and Clock Enable

FPGA device architectures contain registers, also known as "flipflops". The registers in Altera FPGAs provide a number of secondary control signals (such as clear and enable signals) that you can use to implement control logic for each register without using extra logic cells. Device families vary in their support for secondary signals, so consult the device family data sheet to verify which signals are available in your target device.

To make the most efficient use of the signals in the device, your HDL code should match the device architecture as closely as possible. The control signals have a certain priority due to the nature of the architecture, so your HDL code should follow that priority where possible.

Your synthesis tool can emulate any control signals using regular logic, so getting functionally correct results is always possible. However, if your design requirements are flexible in terms of which control signals are used and in what priority, match your design to the target device architecture to achieve the most efficient results. If the priority of the signals in your design is not the same as that of the target architecture, then extra logic may be required to implement the control signals. This extra logic uses additional device resources, and can cause additional delays for the control signals.